XC7Z030-2FFG676I - Circuitus Integrati (IC), Embedded, Systema de Chip (SoC)

Product attributa

| EXEMPLUM | DESCRIPTIO |

| Categoria | Integrated Circuitus (IC) |

| Mfr | AMD |

| Series | Zynq®-7000 |

| sarcina | Tray |

| Product Status | Active |

| Architecture | MCU, FPGA |

| Core Processor | Dual ARM® Cortex®-A9 MPCore™ with CoreSight™ |

| Flash Size | - |

| RAM Location | 256KB |

| Peripherales | DMA |

| Connectivity | CANbus, EBI/EMI, Ethernet, I²C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Celeritas | 800MHz |

| Primaria attributa | Kintex™-7 FPGA, 125K Cellulae Logicae |

| Operating Temperature | -40°C ~ 100°C (TJ) |

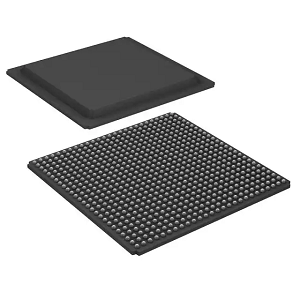

| Sarcina / Case | 676-BBGA, FCBGA |

| Elit Fabrica Package | 676-FCBGA (27x27) |

| Numerus I / O * | 130 |

| Basis Product Number | XC7Z030 |

Documenta & Media

| RESOURCE EXEMPLUM | LINK |

| Datasheets | Zynq-7000 Omnes Programmabiles SoC Overview |

| Product Training Modules | Potentia Series 7 Xilinx FPGAs cum TI Power Management Solutions |

| Environmental Information | Xiliinx RoHS Cert |

| Featured Product | Omnes Programmabiles Zynq®-7000 SoC |

| PCN Design/Specification | Mult Dev Material Chg 16/Dec/2019 |

| Errata | Zynq-7000 Errata |

Environmental & Import Classifications

| TRIBUO | DESCRIPTIO |

| RoHS Status | ROHS3 Compliant |

| Humorem Sensitivity Level (MSL) | 4 (LXXII Horae) |

| SPATIUM Status | SPATIUM Unaffected |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

Application Processor Unit (APU)

Clavis lineamentorum APU includunt:

• Dual-core or single-core ARM Cortex-A9 MPCores.Features consociata cum core includunt:

• 2.5 DMIPS/MHz

• range operating frequency:

- Z-7007S/Z-7012S/Z-7014S (filum vinculum): Usque ad 667 MHz (-1);766 MHz (-2).

- Z-7010/Z-7015/Z-7020 (filum vinculum): Usque ad 667 MHz (-1);766 MHz (-2);866 MHz (-3)

- Z-7030/Z-7035/Z-7045 (flip-chip): 667 MHz (-1);800 MHz (-2);1 GHz (-3)

- Z-7100 (flip-chip): 667 MHz (-1);800 MHz (-2).

• Facultas operandi in uno processu, processus symmetrico, et modos processus asymmetrici dualis.

• Singulus et duplex accurate punctum fluctuetur: usque ad 2.0 MFLOPS/MHz each

• NEON instrumentis processus engine ad SIMD firmamentum

• Thumb®-2 auxilium pressionem codice

• Level 1 cache (disciplinae et notitiae separatae, 32 MB each)

- IV-modo set-associative

- Non-obturans notitia cache cum auxilio usque ad quattuor praestantes legere et scribere misses inter se

• administratio unitatis memoriae Integrated (MMU)

• TrustZone® pro secure modus operandi

• Accelerator cohaerentiae portus (ACP) interfacies ut accessiones cohaerentes a PL ad CPU spatium memoriae

• Unified Level 2 cache (512 KB)

• 8-modo set-associative

• TrustZone enabled ad securam operationem

• Dual-ported, on-chip RAM (256 KB)

• Accessibilis per CPU et logicam programmabilem (PL)

• Designed for low latency access from the CPU

• 8-alveum DMA

• genera translationis multiplex subsidia: ad memoriam, ad memoriam, ad periphericam, periphericam ad memoriam, et colligent.

• 64-bit AXI interfaciei, ut alte perput DMA transferat

canales dicati • 4 PL .

• TrustZone enabled ad securam operationem

• Dual mandare accessum interfaces exigendi separationem inter accessiones securas et non-securas

• obloquitur et Timers

• Interpellare moderatoris Generalis (GIC)

• Tres vigilia canis timers (WDT) (unus per CPU et una ratio WDT)

• Duo ter timers / calculis (TTC)

• CoreSight lusione et vestigium subsidium pro Cortex-A9

• Program macrocell (PTM) ad disciplinam et vestigium

• Cross felis interface (CTI) enabling hardware breakpoints et triggers