Semicon Microcontroller Voltage regulator IC Chips TPS62420DRCR SON10 Electronic Components BOM list service

Product attributa

| EXEMPLUM | DESCRIPTIO |

| Categoria | Integrated Circuitus (IC) |

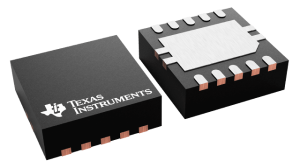

| Mfr | Texas Instrumenta |

| Series | - |

| sarcina | Tape & Reel (TR) Cut Tape (CT) Digi-Reel® |

| SPQ | 3000T&R |

| Product Status | Active |

| Officium | Descenderet reclamantibus |

| Output configurationis | Positivum |

| Acta | Buck |

| Output Type | Product |

| Numerus Outputs | 2 |

| Voltage - Input (Min) | 2.5V |

| Voltage - Input (Max) | 6V |

| Voltage - output (Min/Fixum) | 0.6V |

| Voltage - output (Max) | 6V |

| Current - Output | 600mA, 1A |

| Frequentia - Switching | 2.25MHz |

| Synchroni Rectifier | Ita |

| Operating Temperature | -40°C ~ 85°C (TA) |

| Adscendens Type | Superficie montis |

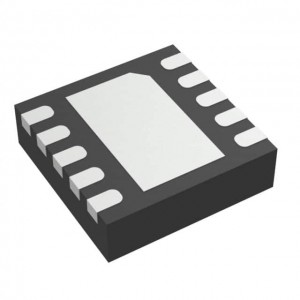

| Sarcina / Case | X-VFDFN Eris Pad |

| Elit Fabrica Package | 10-VSON (3x3) |

| Basis Product Number | TPS62420 |

Conceptus packaging:

Sensus strictus: Processus disponendi, affigendi, et astulae connectendi aliaque elementa in replo vel subiecto technologiae cinematographicae et microfabricationis technicae utendi, ducens ad terminales et eas figendo per malleolum cum medio insulating ad formandum altiorem structuram trium dimensivarum.

Latius loquendo: processus connectendi et figendi sarcinam subiectam, eam congregans in systemate perfecto seu machinae electronicae, et ad effectum totius systematis comprehensivum praestandum.

Munera per chip packaging.

1. munera transferens;2. signa transferendi ambitus;3° providere dissipationis medias caloris;4. Tutela structuris et subsidia.

Artificium technicum de packaging engineering.

Packaging engineering incipit postquam IC chip fit et includit omnes processus antequam chip IC conglutinata et fixa, connexa, encapsulata, obsignata et munita, connexa tabulae ambitui et ratio colligitur usque ad ultimum productum peractum est.

Primus gradus: etiam notus ut fasciculus gradus packaging, est processus figendi, connectendi, et tutandi chip IC ad substratum vel plumbum compagem, faciens modulum (contionis) componentium, quod facile colligi et transportari et connexi potest. ad gradum conventus.

Planum 2: Processus componendi plures fasciculos e gradu 1 cum aliis componentibus electronicis ad cardum ambitum formandum.Gradus 3: Processus combinandi plures chartarum ambitus ex fasciculis in gradu 2 confectis collecti ad componendum vel subsystem in tabula principali formandum.

Gradus 4: Processus congregandi plures subsystematum in electronicum completum.

In chip.Processus connectendi ambitum partium integralium in chip etiam notus est ut fasciculus zephyrus-gradus, ita machinalis packaging etiam per quinque gradus distingui potest.

Genus fasciculorum:

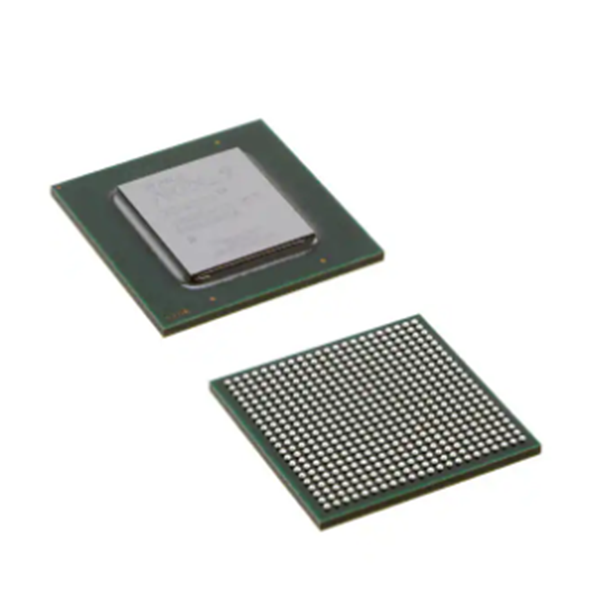

1, secundum numerum astularum IC in fasciculo: involucrum unum chip (SCP) et involucrum multi- chip (MCP).

2, secundum distinctionem materialem signandi: polymerorum materiarum (plasticarum) et ceramicarum.

3, secundum modum instrumenti et circuli tabulae connexionis: clavus insertionis genus (PTH) et genus montanum superficiei (SMT) 4, secundum clavum distribuendi formam: fibulae simplices, fibulae biformes, fibulae quadrilaterae; paxillos deorsum.

SMT machinis L-typum, J-typum habent, et fibulae metallicae I-type.

HAUSTUS : sarcina unius ordinis SQP : involucrum miniaturised MCP : sarcina metallica DIP : sarcina duplicata CSP : involucrum duplicatum QFP : fasciculi quadrati planae PGA : dot involucrum matrix BGA : globus craticula instructa sarcina LCCC : ferebat ceramicam plumbeam