Electronic ic chip Support BOM Service TPS54560BDDAR novam ic chips electronics componentibus

Product attributa

| EXEMPLUM | DESCRIPTIO |

| Categoria | Integrated Circuitus (IC) |

| Mfr | Texas Instrumenta |

| Series | Eco-Modo™ |

| sarcina | Tape & Reel (TR) Cut Tape (CT) Digi-Reel® |

| SPQ | 2500T&R |

| Product Status | Active |

| Officium | Descenderet reclamantibus |

| Output configurationis | Positivum |

| Acta | Buck, Split Rail |

| Output Type | Product |

| Numerus Outputs | 1 |

| Voltage - Input (Min) | 4.5V |

| Voltage - Input (Max) | 60V |

| Voltage - output (Min/Fixum) | 0.8V |

| Voltage - output (Max) | 58.8V |

| Current - Output | 5A |

| Frequentia - Switching | 500kHz |

| Synchroni Rectifier | No |

| Operating Temperature | -40°C ~ 150°C (TJ) |

| Adscendens Type | Superficie montis |

| Sarcina / Case | 8-PowerSOIC (0.154", 3.90mm Latitudo) |

| Elit Fabrica Package | 8-SO PowerPad |

| Basis Product Number | TPS54560 |

1.IC nominatio, sarcina generalis cognitionis et regulae nominationis;

Tortor patens.

C=0°C ad 60°C (gradus commercialis);I=-20°C ad 85°C (gradus industrialis);E=-40°C ad 85°C (gradus industriae extensus);A=-40°C ad 82°C (aerospace gradus);M=-55°C ad 125°C (gradus militaris)

Sarcina genus.

A-SSOP;B-CERQUAD;C-TO-CC, TQFP;D-Ceramic aenea top;E-QSOP;F-Ceramic SOP;II- SBGAJ-Ceramic DIP;K-TO-3;L-LCC, M-MQFP;N-DIP Angusta;N-DIP;Q PLCC;R - Angusta Ceramic DIP (300mil);S - TO-52, T - TO5, TO-99, TO-C;U - TSSOP, uMAX, SOT;W - Lata parva forma factoris (300mil) W-Lata forma parva parva (300 mil);X-SC-60 (3P, 5P, 6P);Aeris angustus y top;Z-TO-92, MQUAD;D-Die;/PR-Plastic aucti;/W-Wafer.

Fibulae numero:

a-8;b-10;c. 12, 192;d-14;e-16;f- XXII, 256;g-4;h-4;i -4;H-4;I-28;J-2;K-5, 68;L-40;M-6, 48;N 18;O-42;P-XX;Q-2, C;R-3, 843;S-4, 80;T-6, 160;U-60 -6,160;U-60;V- 8 (circum);W-X (circum);X-36;Y-8 (circum);Z- 10 (circum).(per).

Nota: Prima littera quattuor litteris suffixis classis interfaciei est E, quae significat fabricam functionis antistaticae habet.

2.Progressio packaging technology

Antiquiores circuli integrati fasciculis ceramicis planis usi sunt, quae a re militari per multos annos propter earum firmitatem et parvitatem adhibita permanebant.Circuitus commercialis fasciculus mox ad sarcinas duplices in linearum transfertur, incipiendo a ceramico et deinde plastico, et in 1980s clavus comitis VLSI circuitus applicationis limites fasciculorum mersa excessit, tandem ad evolutionem craticulam acus vestitus et vectores chippis ducebat.

Superficies montis sarcina in primis 1980s emersit et in posteriore parte illius decennii popularis factus est.Pice tenuiore utitur ac larum alam aut fi acum figuram habet.Circuitus Parvus-Outline (SOIC), exempli gratia, aream 30-50% minus habet et 70% minus crassa est quam aequivalens SUMMERGO.Involucrum hoc larum clavos habet prominentes ex duobus lateribus longi et acum 0.05".

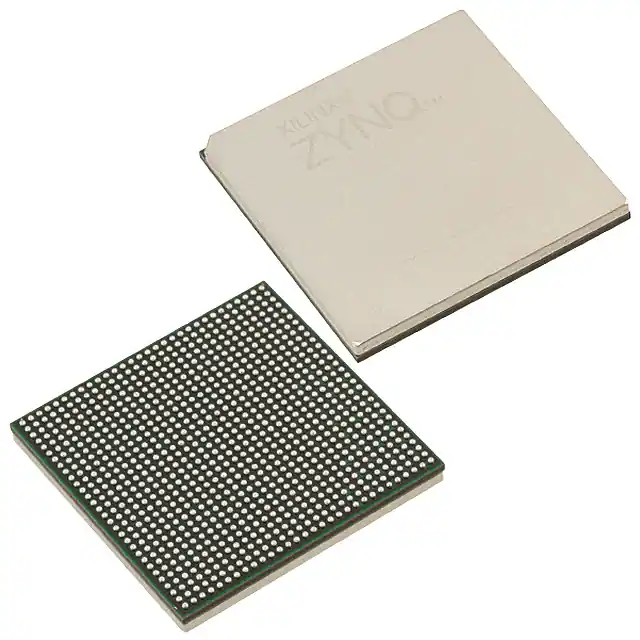

Small Outline Integrated Circuit (SOIC) and PLCC packages.in 1990, quamvis sarcina PGA saepe pro microprocessoribus summus terminus usus est.in PQFP et involucrum parvae-lineae tenue (TSOP) facta est solita sarcina pro clavo magno machinis computatis.Intel et AMD summus finis microprocessores ab PGA (Pine Grid Array) fasciculis ad Land Grid Array (LGA) fasciculis moti sunt.

Fasciculi pila Grid ordinata apparere in annis 1970 coeperunt, et 1990 involucrum FCBGA elaboratum est cum clavo comite superiore quam alii fasciculi.In involucro FCBGA, alea sursum deorsumque flipped et cum globulis solidaribus in fasciculo per PCB quasi basi iacuit potius quam filis connexus.In mercato hodierno, fasciculus nunc etiam separatus processus pars est, et technicae sarcinae qualitatem et fructus operis etiam afficere possunt.