5CEFA7F31I7N novis & originalibus ic xxxiii integratis circuitibus electronicis componendis pretium unum maculam emere BOM servitium

Product attributa

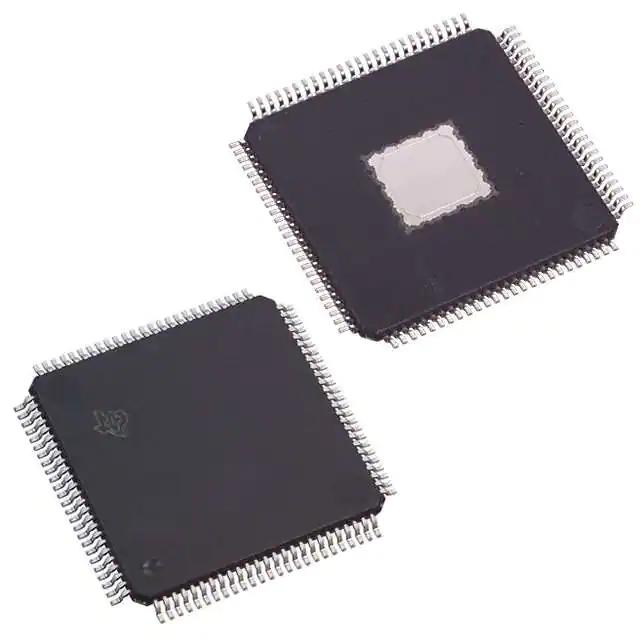

| EXEMPLUM | DESCRIPTIO |

| Categoria | Integrated Circuitus (IC) |

| Mfr | Intel |

| Series | Cyclone® VE |

| sarcina | Tray |

| Latin Package | 27 |

| Product Status | Active |

| Numerus LABS / CLBs | 56480 |

| Numerus Elementorum Logicorum / Cellulae | 149500 |

| Summa RAM Bits | 7880704 |

| Numerus I / O * | 480 |

| Voltage - Supple | 1.07V ~ 1.13V |

| Adscendens Type | Superficie montis |

| Operating Temperature | -40°C ~ 100°C (TJ) |

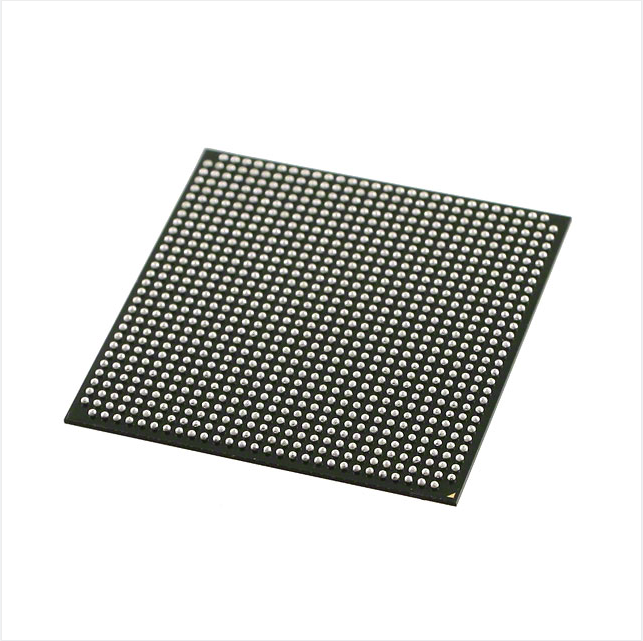

| Sarcina / Case | 896-BGA |

| Elit Fabrica Package | 896-FBGA (31×31) |

| Basis Product Number | 5CEFA7 |

1. Virtex series FPGAs in altum perficientur

Series Virtex est summus finis productum et summum productum in industria Xilinx.Xilinx mercatum vicit cum suis productis Virtex seriei, ita ut FPGA positionem primores elit.Dici potest quod Xilinx portam programmabilem portam camporum ordinatam industriam ducit cum sua Virtex familia FPGA productorum.Maxime intenduntur applicationes sicut infrastructura telecomes, industria autocinetica, et summus finis electronicarum dolor.Praesens amet astulae includunt Vitrex-2, Virtex-2 Pro, Virtex-4, Virtex-5, Virtex-6, et Virtex 7 Genera.

Virtex-2 series in 2002 cum processu 0.15nm introducta est, 1.5V core intentionum, horologiorum operantium usque ad 420MHz, subsidium plus quam XX I/O signa interfaciendi, plena ratio horologii administrationis facultatum, et in IP core dura constructa. nuclei technologiae quae dura IP nuclei ubique in chip assignari permittit, cum pluribus opibus et altiori observantia quam series Virtex.nobilior effectus quam Virtex familia.

Virtex-2 Pro series in Virtex-2 constructis processui facultatibus auctis, PowerPC405 nucleis immersis, technologiam activam Interconnectorum provectam includit, ut provocationes e rationibus agendi rationum praealtae, praeter accessionem altae celeritatis, includat. Vide transceiver ad Gigabit Ethernet solutiones praebere.

Virtex-4 familia fundata est ex deducto Module (ASMBL) architecturae Provectae Siliconis Clausae, quae summam logicam notat densitatem cum frequentiis horologii usque ad 500 MHz;cum DCM modulis, PMCD phase adaptatio horologii circini, in retiacula differentialia horologii;D MHz SmartRAM technologiae cum FIFO potestate logicae integrata, et unaquaeque I/O cum Chipsync fonte synchronisationi technologiae integratur pro 1 Gbps I/O et Xtreme DSP logicae chip.Designatores possunt eligere diversas Virtex-4 subsystems secundum necessitates suas, ad intensiva consilia logica: Virtex-4 LX, ad altum faciendum signum applicationes processus: Virtex-4 SX, ad celeritatem Vide connectivity et in applicationes processus infixae: Virtex- 4 fx.Virtex-4 familia insignem emendationem praebet in omnibus metricis super VirtexII. Virtex-4 series, quae in massa productione ab fine anni 2005 facta est, VirtexII, VirtexII-Pro substituit, et Xilinx maximum momentum in alto hodierno productum est. -end forum FPGA.

Familia Virtex-5 in statu-of-arte 65nm technologiae aeris innititur et in secunda generatione ASMBL (Advanced Silicon Building Block) architectura columnaris, quinque suggesta distincta (subfamiliae) continens.Unumquodque suggestum varias continet rationes ad quae exigentiis multorum logicorum provectorum occurrentium.Praeter statum architecturae artis summus perficientur logicae, Virtex-5 FPGAs varias includunt modulorum durorum IP systematis gradus, in quibus potens 36 Kb Block RAM/FIFO, generationis secundae 25×18 DSP Verre, SelectIO technologia cum in CNC impedimento constructa, Chipsync fons synchronisationi modulorum interfaceti, ratio monitoris functionis, et integra DCM (Procurator horologii digitalis) et PLL (Phase Locked Loop) horologium generantium, et optiones conformationis provectae.Aliae notae suggestae fundatae includunt potestatem optimized summus velocitatis Vide moduli transceiveri ad auctam serialem connectivity, PCI Express-compatible terminus moduli integralis, a tri-state Ethernet MAC (media accessus controller), et summus perficientur PowerPC 440 microprocessor modulus immersus, qui efficit ut excogitatores logicae provectae involvant summos gradus agendi in systematis suis FPGA fundatis.

Familia Virtex-6 offert notas novissimas, antecedens in foro FPGA.Virtex-6 FPGAs sunt programmabiles technologiae siliconis fundamenta pro testbeds target quae praebent ferramenta et programmata ad adiuvandum designatores ut focus in innovatione semel evolutionis conatus initiati sunt.Virtex-6 notae familiares ASMBL tertia generatio (promovit moduli portfolio Pii) columna architectura quae varias subfamilias continet.Haec descriptio machinas in LXT, SXT, HXT subfamilias describit.Unaquaeque familia continet diversas lineas iuncturas ut efficaciter occurrat amplis progressibus consiliorum logicarum requisitis.Praeter fabricae logicae summus observantia, Virtex-6 FPGAs plures in systematis gradu modulorum constructis comprehendunt.Haec lineamenta logicae designantes efficiunt ut supremas gradus perficiendi et functionis in suas FPGA systemata construant.Virtex-6 FPGAs etiam optimam solutionem praebent ad usus necessarios summus faciendorum logicorum designatores, summus operandi DSP designatores, et summus effectus infixa ratio designantium, quae inaudita logica, DSP, connectivity, et mollis microprocessoris facultates afferunt.

Virtex-7 est ultra summus finis FPGA productus introductus in 2011 in 28nm processus, qui dat clientibus libertatem ligandi et solvendi notas quae sumptus et potentiam minuunt consumptio dum perficiendi et augendi facultatem, minuendo evolutionem et instruere collocationes utriusque humilitatis. -cost familias et summus perficientur.Praeterea, 35% deminutio sumptus ad Virtex-6 comparata cavetur nulla conversione incrementali vel collocatione machinalis, augendo productivitatem amplius.

.png)