VISERE originalis et novos ambitus electronicarum partium XC2VP50-6FF1152I

Product attributa

| EXEMPLUM | DESCRIPTIO |

| Categoria | Integrated Circuitus (IC) |

| Mfr | Intel Xilinx |

| Series | Virtex®-II Pro |

| sarcina | Tray |

| Product Status | Obsoletum |

| Numerus LABS / CLBs | 5904 |

| Numerus Elementorum Logicorum / Cellulae | 53136 |

| Summa RAM Bits | 4276224 |

| Numerus I / O * | 692 |

| Voltage - Supple | 1.425V ~ 1.575V |

| Adscendens Type | Superficie montis |

| Operating Temperature | -40°C ~ 100°C (TJ) |

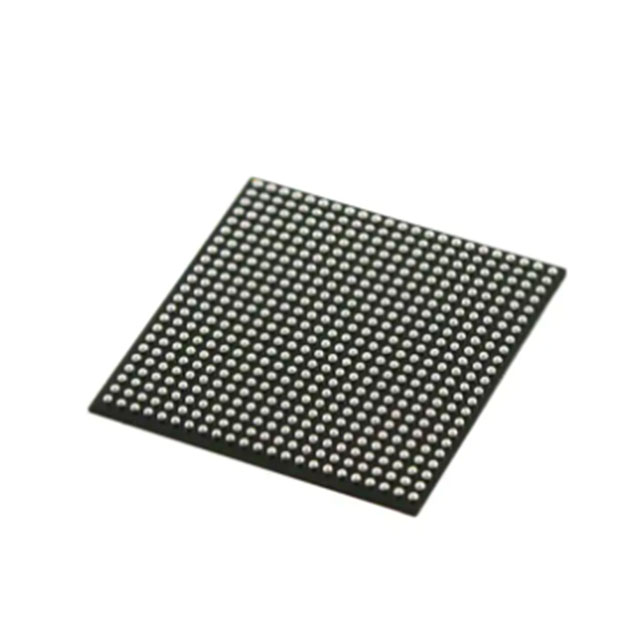

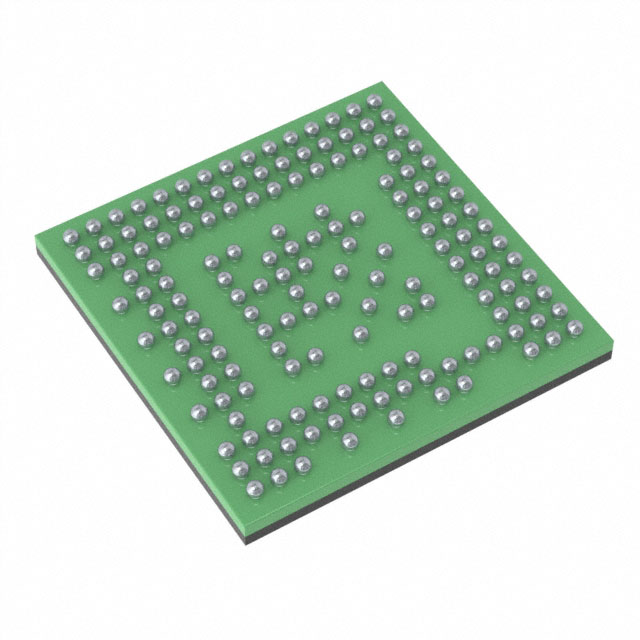

| Sarcina / Case | 1152-BBGA, FCBGA |

| Elit Fabrica Package | 1152-FCBGA (35×35). |

| Basis Product Number | XC2VP50 |

Documenta & Media

| RESOURCE EXEMPLUM | LINK |

| Datasheets | Virtex-II Pro, Pro X |

| Environmental Information | Xiliinx RoHS Cert |

| PCN Obsolescene/EOL | Mult Dev EOL 6/Jan/2020 |

| HTML Datasheet | Virtex-II Pro, Pro X |

| EDA exemplum | XC2VP50-6FF1152I by Ultra Librarian |

Environmental & Import Classifications

| TRIBUO | DESCRIPTIO |

| RoHS Status | RoHS non facilis |

| Humorem Sensitivity Level (MSL) | 4 (LXXII Horae) |

| SPATIUM Status | SPATIUM Unaffected |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

XC2VP50-6FF1152I FPGAs Overview

Virtex-II Pro et Virtex-II Pro X familias suggestum continent FPGAs ad designationes quae in nucleis IP nituntur et modulorum nativus.XC2VP50-6FF1152I incorporat multi transceivers et PowerPC CPU clausos in Virtex-II Pro Series FPGA architecturae.Soluciones telecommunicationi, wireless, networking, video, DSP applicationes completas dat.

Ora primores 0.13 µm CMOS novenarii processus aeris et Virtex-II Pro architectura optimizantur ad alta consilia facienda in amplis densitatibus.Coniungens varietatem lineamentorum flexibilium et nucleorum IP, XC2VP50-6FF1152I auget facultatem consiliorum programmabilem logicam et potens est alternare ut portae larva-programma vestit.

Series Xilinx Industrialis XC2VP50-6FF1152I est 53136 Cellae Logicae 16 Eruca IOs 2 Potentia, Visum Substituta & Alternativa cum data sheets, copia, pricing ab Authorised Distributores ad FPGAkey.com, et etiam quaerere potes alias FPGAs productas.

Features

Summus euismod Platform FPGA Solutio, Complectens

Usque ad viginti RocketIO aut RocketIO X embedded Multi-Gigabit Transceivers (MGTs)

Ad duo IBM PowerPC RISC processus cuneos

Ex Virtex-II Platform FPGA Technology

Facultates flexibiles logicae

SRAM-fundatur in-ratio configuratione

Active Interconnect technology

SelectRAM+ hierarchiae memoriam

Dedicavit XVIII frenum x XVIII-bit multiplicator caudices

Summus horologium procuratio ambiens

SelectI/O-technologia Ultra

XCITE Digitally Controlled Impedimentum (DCI) I / O *