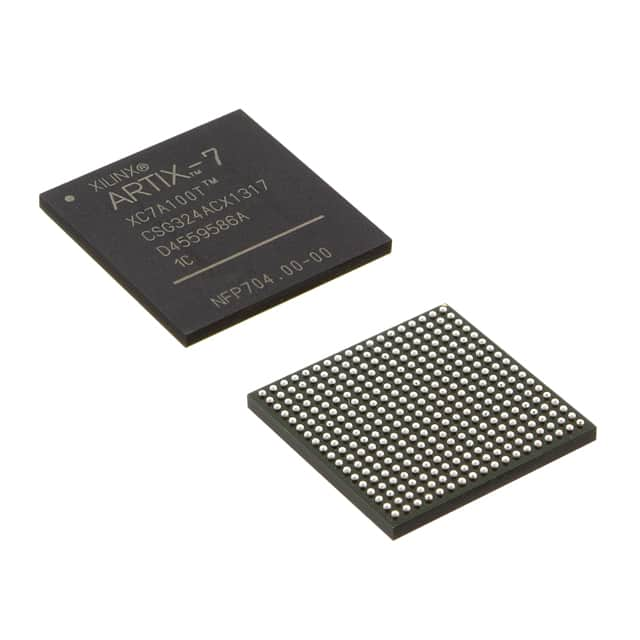

Originale IC chip Programmabile XCVU440-2FLGA2892I IC FPGA 1456 I/O 2892FCBGA

Product attributa

| EXEMPLUM | DESCRIPTIO |

| Categoria | Integrated Circuitus (IC) |

| Mfr | Intel Xilinx |

| Series | Virtex® UltraScale™ |

|

| Box |

| Standard Package | 1 |

| Product Status | Active |

| Numerus LABS / CLBs | 316620 |

| Numerus Elementorum Logicorum / Cellulae | 5540850 |

| Summa RAM Bits | 90726400 |

| Numerus I / O * | 1456 |

| Voltage - Supple | 0.922V ~ 0.979V |

| Adscendens Type | Superficie montis |

| Operating Temperature | -40°C ~ 100°C (TJ) |

| Sarcina / Case | 2892-BBGA, FCBGA |

| Elit Fabrica Package | 2892-FCBGA (55×55) |

| Basis Product Number | XCVU440 |

Per FPGAs ut negotiationis processors ad network securitatem

Negotiatio huc et a securitate machinarum (firewalls) in multiplicibus gradibus encryptur, et L2 encryption/decryption (MACSec) discursum est ad ligamen tabulatum (L2) retis nodis (switches et iter itineris).Processus ultra L2 (MAC layer) typice includit parsing profundiorem, cuniculum decryptionem L3 (IPSec), et encryptatum SSL commercii cum TCP/UDP negotiationis.Processus fasciculus implicat parteming et classificationem ineuntes fasciculos et processus magnorum librorum negotiationis (1-20M) cum alto throughput (25-400Gb/s).

Ob magnum numerum computandi facultates (cores) requisiti, NPUs adhiberi potest ad processus altioris celeritatis fasciculus, sed humilis latency, summus effectus processus mercaturae scalabiles non possibilis est quia negotiatio discursum est utens MIPS/RISC nucleos et scheduling tales metretas fundatur in promptu difficile.Usus instrumentorum securitatis FPGA fundatae potest has limitationes CPU et NPU substructas architecturas efficaciter tollere.

Applicationem-gradu securitatis processus in FPGAs

FPGAs ideales sunt ad inlineationem securitatis processus in altera-generatione ignium ignium, quia feliciter occurrent ad altiorem observantiam, flexibilitatem, et humilitatis latentiam operandi necessitatem.Praeterea FPGAs etiam efficere possunt functiones securitatis applicationis graduum, quae amplius servare facultates computantes et exsequendum emendare possunt.

Exempla communia applicationis securitatem processus in FPGAs includunt

- TTCP offload engine

- Ordinarius expressio matching

- Asymmetric encryption (PKI) processus

- TLS processus

Postero-generatio securitatis technologiae utens FPGAs

Multae algorithmorum asymmetricarum exsistentium in quantis computatoribus vulnerari possunt.Securitas asymmetrica algorithms ut RSA-2K, RSA-4K, ECC-256, DH, ECCDH sunt affecti quantis technicis computandis.Novae exsecutiones algorithmorum asymmetricorum et normae NIST explorantur.

Current propositiones pro post-quantum encryption includunt anulum in Error Doctrinae (R- LWE) methodum pro

- Clavis Publica Cryptographiae (PKC)

- Digital subscriptionibus

- Key creaturae

Proposita exsecutio cryptographiae publicae clavium includunt operationes quasdam notissimas mathematicas (TRNG, Gaussian strepitus sampler, polynomiae additionis, polynomiae quantitatis binarii divisionem, multiplicationem, etc.).FPGA IP multis ex his algorithms in promptu est vel efficaciter perfici potest utens FPGA structurae caudices, ut machinas DSP et AI (AIE) in exsistentibus et proximis machinis Xilinx.

Haec charta alba exsecutionem securitatis L2-L7 describit utens architecturae programmabilis quae explicari potest ad securitatem accelerationis in ore/retis accessu et ignium generationis sequentium (NGFW) in retiaculis inceptis.