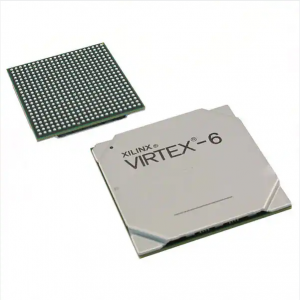

Nova et originalia XC6VLX240T-2FFG1759I Integrated circuit

Product attributa

| EXEMPLUM | DESCRIPTIO |

| Categoria | Integrated Circuitus (IC) |

| Mfr | Intel Xilinx |

| Series | Virtex®-6 LXT |

| sarcina | Tray |

| Product Status | Active |

| Numerus LABS / CLBs | 18840 |

| Numerus Elementorum Logicorum / Cellulae | 241152 |

| Summa RAM Bits | 15335424 |

| Numerus I / O * | 720 |

| Voltage - Supple | 0.95V ~ 1.05V |

| Adscendens Type | Superficie montis |

| Operating Temperature | -40°C ~ 100°C (TJ) |

| Sarcina / Case | 1759-BBGA, FCBGA |

| Elit Fabrica Package | 1759-FCBGA (42.5×42.5) |

| Basis Product Number | XC6VLX240 |

Documenta & Media

| RESOURCE EXEMPLUM | LINK |

| Datasheets | Virtex-6 FPGA Datasheet |

| Product Training Modules | Virtex-6 FPGA Overview |

| Environmental Information | Xiliinx RoHS Cert |

| PCN Design/Specification | Crux-Navis Plumbum-Free Notitia 31/Oct/2016 |

Environmental & Import Classifications

| TRIBUO | DESCRIPTIO |

| RoHS Status | ROHS3 Compliant |

| Humorem Sensitivity Level (MSL) | 4 (LXXII Horae) |

| SPATIUM Status | SPATIUM Unaffected |

| ECCN | 3A001A7A |

| HTSUS | 8542.39.0001 |

XC6VLX240T-2FFG1759I FPGAs Overview

XC6VLX240T-2FFG1759I FPGAs sunt fundamenta programmabilis siliconis pro Targeted Design Platforms, quae integrationem programmatis et ferramentis tradent, ut designatores ad innovationem intendunt quam primum cycli evolutionis cycli initium facere possint.Per tertiam generationem ASMBL (Silicon Clausus Modularis Progressus) Architectura columnarum substructio, Xilinx XC6VLX240T-2FFG1759I multas systematis-gradus caudices constructi continent.Haec lineamenta logicae permittunt designatores ad summos gradus perficiendi et functionis faciendos in systemata sua FPGAbased aedificare.Constructum in 40 um statu-of-artis processus technologiae aeris, XC6VLX240T-2FFG1759I FPGAs programmabiles sunt ad technologiam technologiae ASIC.optimam solutionem offerre ad explicandas necessitates summus operandi logicae designatores, summus operandi DSP designatores, ac summus effectus infixa rationum designantium cum inusitata logica, DSP, connectivity, et microprocessoris facultatibus mollibus.

Xilinx FPGAs (Ges Programmabilis Porta Array) series XC6VLX240T-2FFG1759I est Virtex-6 LXT FPGA 720 I/O 1759FCBGA, Visum substitutorum & alternativarum cum data schedae, copia, pricing ab Authorised distributoribus apud FPGAkey.com, et etiam quaerere potes alia FPGAs producta.

Features

Tres familiae sub-;

Virtex-6 LXT FPGAs: Summus perficientur logica cum provecta Vide connectivity

Virtex-6 SXT FPGAs: Altissimum signum processui facultatem cum provectis Vide connectivity

Virtex-6 HXT FPGAs: Altissimum Sed Vide connectivity

Compatibility per sub-familias

LXT et SXT strophas vestigium compatiuntur in eadem sarcina

Provectus, summus perficientur FPGA Logica

Verus VI-input vultus-sursum mensam (LUT) technology

Dual LUT5 (5-input LUT) option

LUT/dual flip-flop par pro applicationibus requirunt dives mandare mix

Improved profectus efficientiam

64-bit (vel duas 32-bit) distributa optio LUT RAM per 6-input LUT

SRL32/ dual SRL16 cum descripserunt outputs optionem

Horologium magistri potentissimi mixti-modus (MMCM)

MMCM cuneos praebent nullae morae buffering, frequentiam synthesim, horologium mobilem, inputjittere eliquationem, et periodum horologii congruentem divisionem.

36-Kb obstructionum RAM/FIFOs

Princeps perficientur parallel SelectIO technology

Provectus DSP48E1 crustae

Flexibile configuratione optiones

SPI et Parallel Flash interface

Multi- bitstream subsidium cum dicato fallback reconfigurationis logicae

Lorem latitudo bus deprehendatur

Ratio Monitor facultatem in omnibus artibus

On-chip/off-chip scelerisque ac copia intentione magna

JTAG aditum omnibus quantitatis viverra

Integrated interface cuneos ad PCI designs

GTX transceivers: usque ad 6.6 Mb/s

Datae rates infra 480 Mb/s in FPGA logica transfundendo suffulta.

GTH transceivers: 2.488 Mb/s ultra 11 Mb/s

Integrated 10/100/1000 Mb/s Ethernet MAC scandalum

Sustinet 1000BASE-X PCS/PMA et SGMII utentes GTX transceivers

MII, GMII, et RGMII subsidiis technologiae adhibitis

2500Mb/s auxilium available

40 nm aeris CMOS processus technologiae

1.0V core intentione (1, -2, -3 gradus tantum velocitatis)

Inferioris potentiae 0.9V core voltage optio (1L celeritate gradus only)

Princeps signum integritatis flip-chip packaging available in vexillum vel Pb-liberum sarcina optiones